|

|

UInt32 | DeAd |

| | Device address.

|

| |

|

UInt32 | ClAd |

| | Clock address.

|

| |

|

UInt32 | ClVa |

| | Clock value (defaults to 2 = enabled, set to 0 = disabled).

|

| |

|

UInt32 | REVISION |

| | Register at offset 00h (see ARM Reference Guide, chapter 12.5.1.1 ).

|

| |

|

UInt32 | SYSCONFIG |

| | Register at offset 10h (see ARM Reference Guide, chapter 12.5.1.2 ).

|

| |

|

UInt32 | IRQSTATUS_RAW |

| | Register at offset 24h (see ARM Reference Guide, chapter 12.5.1.3 ).

|

| |

|

UInt32 | IRQSTATUS |

| | Register at offset 28h (see ARM Reference Guide, chapter 12.5.1.4 ).

|

| |

|

UInt32 | IRQENABLE_SET |

| | Register at offset 2Ch (see ARM Reference Guide, chapter 12.5.1.5 ).

|

| |

|

UInt32 | IRQENABLE_CLR |

| | Register at offset 30h (see ARM Reference Guide, chapter 12.5.1.6 ).

|

| |

|

UInt32 | IRQWAKEUP |

| | Register at offset 34h (see ARM Reference Guide, chapter 12.5.1.7 ).

|

| |

|

UInt32 | DMAENABLE_SET |

| | Register at offset 38h (see ARM Reference Guide, chapter 12.5.1.8 ).

|

| |

|

UInt32 | DMAENABLE_CLR |

| | Register at offset 3Ch (see ARM Reference Guide, chapter 12.5.1.9 ).

|

| |

|

UInt32 | CTRL |

| | Register at offset 40h (see ARM Reference Guide, chapter 12.5.1.10 ).

|

| |

|

UInt32 | ADCSTAT |

| | Register at offset 44h (see ARM Reference Guide, chapter 12.5.1.11 ).

|

| |

|

UInt32 | ADCRANGE |

| | Register at offset 48h (see ARM Reference Guide, chapter 12.5.1.12 ).

|

| |

|

UInt32 | ADC_CLKDIV |

| | Register at offset 4Ch (see ARM Reference Guide, chapter 12.5.1.13 ).

|

| |

|

UInt32 | ADC_MISC |

| | Register at offset 50h (see ARM Reference Guide, chapter 12.5.1.14 ).

|

| |

|

UInt32 | STEPENABLE |

| | Register at offset 54h (see ARM Reference Guide, chapter 12.5.1.15 ).

|

| |

|

UInt32 | IDLECONFIG |

| | Register at offset 58h (see ARM Reference Guide, chapter 12.5.1.16 ).

|

| |

|

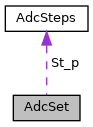

AdcSteps | St_p [16+1] |

| | step configuration (see ARM Reference Guide, chapter 12.5.1.17 ff, charge step + 16 steps, by default steps 1 to 8 are used for AIN-0 to AIN-7).

|

| |

|

UInt32 | FIFO0COUNT |

| | Register at offset E4h (see ARM Reference Guide, chapter 12.5.1.51 ).

|

| |

|

UInt32 | FIFO0THRESHOLD |

| | Register at offset E8h (see ARM Reference Guide, chapter 12.5.1.52 ).

|

| |

|

UInt32 | DMA0REQ |

| | Register at offset ECh (see ARM Reference Guide, chapter 12.5.1.53 ).

|

| |

|

UInt32 | FIFO1COUNT |

| | Register at offset F0h (see ARM Reference Guide, chapter 12.5.1.54 ).

|

| |

|

UInt32 | FIFO1THRESHOLD |

| | Register at offset F4h (see ARM Reference Guide, chapter 12.5.1.55 ).

|

| |

|

UInt32 | DMA1REQ |

| | Register at offset F8h (see ARM Reference Guide, chapter 12.5.1.56 ).

|

| |

Structure for ADC subsystem registers.

This UDT contains a set of all ADC subsystem registers. It's used to store the initial configuration of the subsystem and to hold current configuration for the next call to function PruIo::config().

- Since

- 0.2

Definition at line 36 of file pruio_adc.bi.